CMOS on-chip thermometry at deep cryogenic temperatures

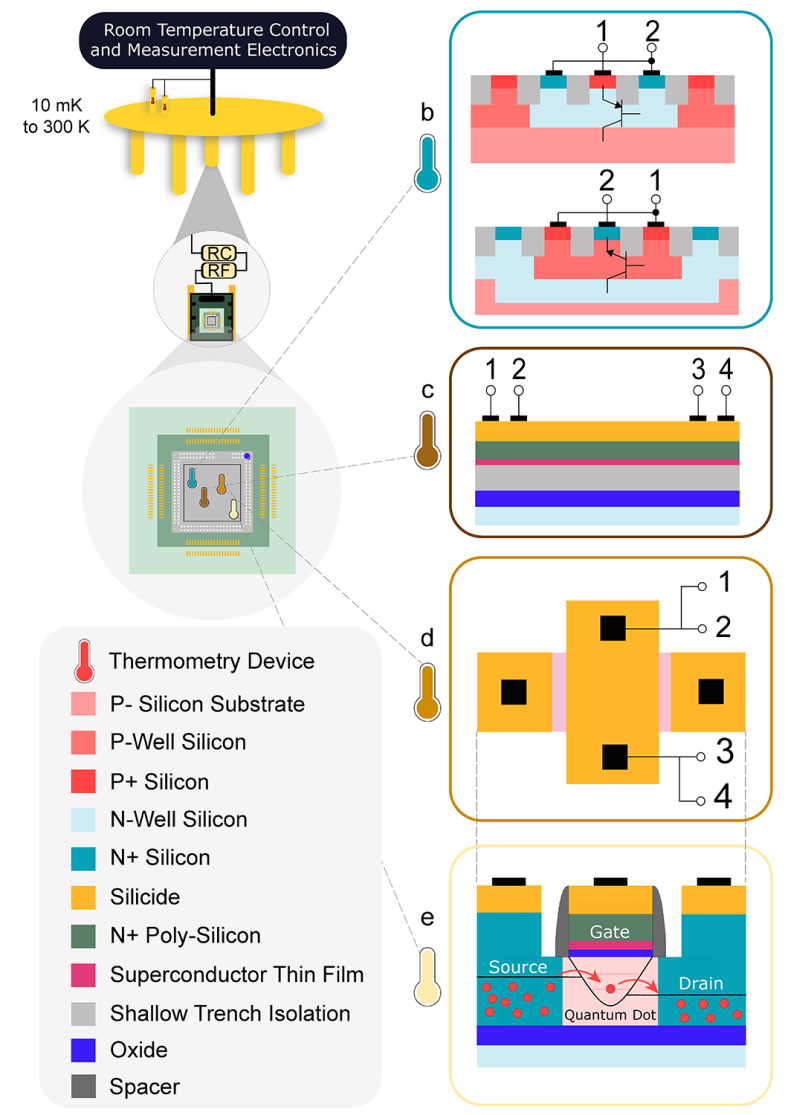

Diagram of cryogenic measurement setup. The legend in the bottom left gives the materials in the structures used for thermometry(b)-(e)..

The microprocessors in your computer come embedded with temperature sensors, to ensure the CPU doesn’t overheat. Similar on-chip sensors need to be developed for solid-state quantum processors, but these have the additional challenge of working at the ultra low temperatures needed for quantum computing.

Our team at Quantum Motion has shown that diode thermometry enables sensitive thermometry well below 1.5 K, the common lower limit for commercial cryogenic diode thermometers. We found that diode thermometry can have significant temperature sensitivity maintained down to 100 mK.

Our team has developed and benchmarked four methods of CMOS on-chip thermometry that operate at milliKelvin temperatures. We found that diode thermometry (DT), particularly when biased with a low current (1 nA), is the most sensitive method when compared to gate resistance thermometry (GRT), superconducting phase transition thermometry (SPTT) and quantum dot thermometry (QDT) for the whole temperature range studied (20 mK to 300 K). We envision that the sensitivity of the DT technique could be improved further by operating the sensor in conjunction with fast readout techniques.

The team also showed that we can use the superconductivity of the gate stack, effectively an SPTT measurement, to capture the on-chip temperature. We refer to it as superconducting gate resistance thermometry (SGRT).

All the methods have the ability to be integrated in scaled-up circuits, helping us build towards our goal of a scalable quantum silicon processor.

The Quantum Motion team that achieved this work includes: Grayson Noah, Thomas Swift, Mathieu de Kruijf, Alberto Gomez-Saiz, John J. L. Morton, and M. Fernando Gonzalez-Zalba.