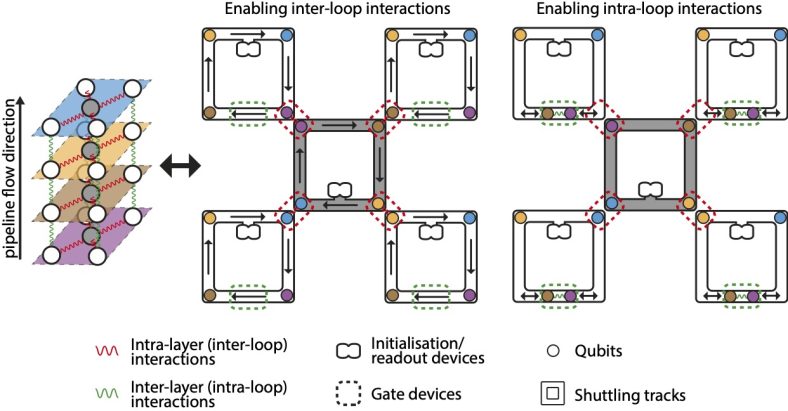

Looped Pipelines Enabling Effective 3D Qubit Lattices in a Strictly 2D Device

We have identified an architecture that enables the implementation of a 3D qubit lattice in a 2D hardware platform, which opens up doors to a wide range of applications that were previously constrained by qubit connectivity. In particular, we found that it can remove almost all overheads for a leading quantum error mitigation method in near-term quantum applications. For applications further down the road, it can reduce the overhead of the leading fault-tolerant approach by up to two orders of magnitude.